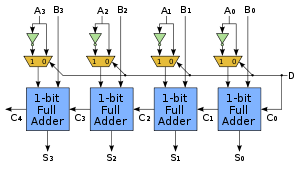

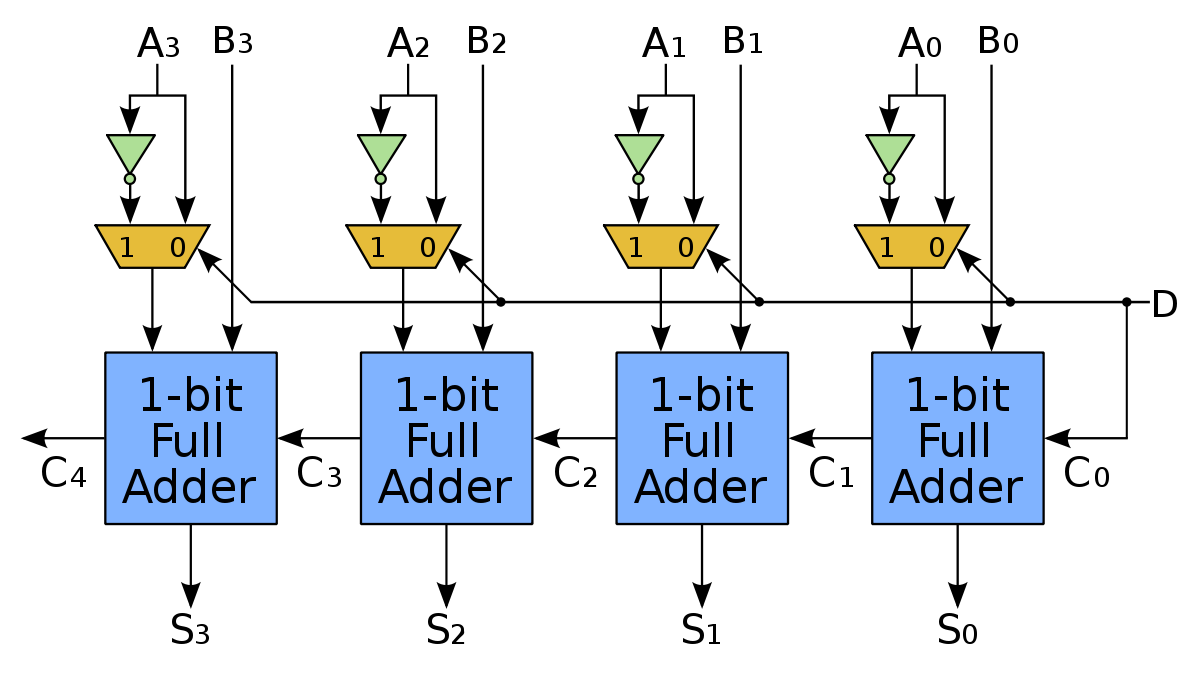

Parity generator with serial input and parallel.VHDL for Arithmetic Functions and Circuits. 16-bit adder/subtractor. Here is a hardware description of a multiplier If B[0].traffic light verilog code on FPGA, verilog code for traffic light controller,. Verilog code for Multiplier. VHDL projects // Verilog code for carry look-ahead adder module cpu_wb_cla_adder (in1, in2, carry_in, sum. Verilog code for Arithmetic Logic Unit (ALU) Last time, an Arithmetic Logic Unit ( ALU ) is designed and implemented in VHDL. Full VHDL code for the ALU was presented. Full-Adder in Verilog Review. A full adder is a combinational logic that takes 3 bits, a, b. All we need to do is write Verilog code that will replicate the full-adder encapsulated in SingleStage 4 times. // vars integer i; // Instantiate the Unit Under Test (UUT) MultiStages uut (. Write the verilog code for a Full Adder, that takes in three 1-bit inputs, a, b. 5.6 Write the hardware description of a 4-bit adder/subtractor and test it. EE Summer Camp 2006 Verilog Lab Solution File Pointers. Similarly, given the two 4–bit numbers 1011 and 0110, the serial adder starts by adding 1 plus 0 equal to 1, and then 1 plus 1 equal to 10 (place 0 and carry the 1), and so on. For a general demonstration, both a human person and a serial adder follow the same sequential method.

Active3 years, 7 months ago

$begingroup$

I am trying to write the test bench part but I don't know how to do it. Basically, I want to test out 0x10 or 5x5. I don't if what I have is right.

• Click 'Yes' to confirm the uninstallation. How do I uninstall Cute PDF Writer in Windows 95, 98, Me, NT, 2000? • Click 'Start' • Click on 'Control Panel' • Click the Add or Remove Programs icon. Jefazo martin sivak pdf writer. • Click on 'Cute PDF Writer', then click 'Remove/Uninstall.' How do I uninstall Cute PDF Writer in Windows XP?

here's a pic to give you some idea of what i am trying to build. it is not this exact one.

Here is the full adder:

Here is the multiplier: Epsxe cheat download.

Here is my test bench:

CharleBarkely123CharleBarkely123

$endgroup$1 Answer

$begingroup$

Half Adder Verilog Code

I do not understand why in a 4 bit x 4 bit multiplier you are taking 4 inputs that also of 8 bit, what are they representing. If it is a combinational logic multiplier it should have been:

Full Subtractor Verilog

Purnendu KumarPurnendu Kumar

$endgroup$